## SANYO Semiconductors

## DATA SHEET

# LC723341E -ETR Controller

## **Overview**

The LC723341E is a single-chip microcontroller/electronic tuner that also integrates a 250 MHz PLL circuit and a 1/4-duty 1/2-bias LCD driver on the same chip.

## **Functions**

- Program memory (ROM): 4096 × 16 bits (8 KB)

- Data memory (RAM):  $256 \times 4$  bits

- Cycle time: 1.33 µs (all one-word instructions) at 4.5 MHz

- Stack: 8 levels

- LCD driver: 48 to 80 segments (1/4-duty 1/2-bias drive)

- Interrupts: External interrupts: 2 systems

- Timer interrupts: 2 systems (1, 5, 10 or 50 ms)

- A/D converter: Four input channels (6-bit successive approximation conversion)

- Dedicated input ports: 8 ports (of which 4 can be switched for use as A/D converter inputs)

- Dedicated output ports: 10 ports (of which 6 are open-drain ports and 4 can be switched between CMOS and opendrain specifications)

- I/O ports: 19 ports (of which 8 can be switched for use as segment ports)

- PLL: Reference frequencies: 3, 3.125, 5, 6.25, 12.5 and 25 kHz

- Supports dead zone control (4 types) and features a built-in unlock detection circuit.

- Input frequency (input sensitivity): FM band 10 to 250 MHz

#### AM band- 0.5 to 40 MHz

• Input sensitivity: FM band - 35 mV rms (Above 130 MHz: 50 mV rms)

AM band - 35 mV rms

- IF counting: HCTR input 0.4 to 12 MHz (35 mV rms)

- External reset input: The program counter starts from location 0 during CPU and PLL operation

- Reset: Built-in voltage detection reset circuit

- Halt mode: The controller's operating clock is temporarily slowed to reduce current drain.

- Backup mode: The crystal oscillator is stopped.

- Static power on function: Backup mode is cleared using the PF port.

- Beep tone: Frequencies of 0.75, 1.25, 1.5, 2.08. 2.5, 3.125, and 6.25 kHz

- Memory retention voltage: 0.9 V or higher

- VDD: PLL 4.5 to 5.5 V

- CPU 3.5 to 5.5 V

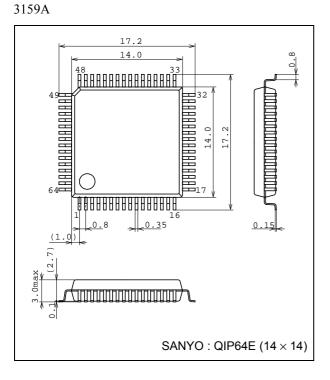

- Package: QIP64E (0.8 mm pitch)

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

#### SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

## Specifications

## Absolute Maximum Ratings at Ta = 25°C, $V_{SS} = 0 V$

| Parameter                   | Symbol              | Conditions                   | Ratings             | Unit |

|-----------------------------|---------------------|------------------------------|---------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |                              | -0.3 to +6.5        | V    |

| Input voltage               | VIN                 | All input pins               | -0.3 to VDD to +0.3 | V    |

| Output voltage              | V <sub>OUT</sub> 1  | PE2, PL0 to PL3              | –0.3 to +15         | V    |

| Output voltage              | V <sub>OUT</sub> 2  | All output pins except VOUT1 | -0.3 to VDD + 0.3   | V    |

|                             | IOUT1               | PC, PD, PE3, PG, PH, PK, EO  | 0 to 3              | mA   |

|                             | IOUT2               | PB                           | 0 to 1              | mA   |

| Output current              | I <sub>OUT</sub> 3  | PE2, PL0 to PL3              | 0 to 2              | mA   |

|                             | IOUT4               | S1 to S20                    | 0 to 1              | μΑ   |

|                             | IOUT5               | COM1 to COM4                 | 3                   | mA   |

| Allowable power dissipation | Pdmax               | Ta = -20 to +70°C            | 300                 | mW   |

| Operating temperature       | Topr                |                              | -20 to +70          | °C   |

| Storage temperature         | Tstg                |                              | -45 to +125         | °C   |

## Package Dimensions

unit: mm

| Parameter                | Symbol            | Conditions                                                                                  | Ratings            |     |                    | Unit |

|--------------------------|-------------------|---------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| Parameter                | Symbol            | Conditions                                                                                  | min                | typ | max                | Unit |

|                          | V <sub>DD</sub> 1 | PLL operating voltage                                                                       | 4.5                |     | 5.5                |      |

| Supply voltage           | V <sub>DD</sub> 2 | Memory retention voltage                                                                    | 0.9                |     | 5.5                | V    |

|                          | V <sub>DD</sub> 3 | CPU operating voltage                                                                       | 2.6                |     | 5.5                |      |

|                          | VIH1              | Input ports other than $V_{IH}2,V_{IH}3,\text{AMIN},\text{FMIN},\text{HCTR},\text{and}$ XIN | 0.7V <sub>DD</sub> |     | V <sub>DD</sub>    | V    |

| High-level input voltage | VIH2              | BRES                                                                                        | 0.8V <sub>DD</sub> |     | VDD                | V    |

|                          | V <sub>IH</sub> 3 | The PF port                                                                                 | 0.6V <sub>DD</sub> |     | V <sub>DD</sub>    | V    |

|                          | VIL1              | Input ports other than $V_{IL}2,V_{IL}3,AMIN,FMIN,HCTR,andXIN$                              | 0                  |     | 0.3V <sub>DD</sub> | V    |

| Low-level input voltage  | VIL2              | BRES                                                                                        | 0                  |     | 0.2V <sub>DD</sub> | V    |

|                          | V <sub>IL</sub> 3 | The PF port                                                                                 | 0                  |     | 0.2V <sub>DD</sub> | V    |

|                          | VIN1              | XIN                                                                                         | 0.5                |     | 1.5                | Vrms |

| Innut amplitude          | V <sub>IN</sub> 2 | FMIN: F <sub>IN</sub> 2, AMIN                                                               | 0.035              |     | 0.35               | Vrms |

| Input amplitude          | V <sub>IN</sub> 3 | FMIN: F <sub>IN</sub> 3                                                                     | 0.05               |     | 0.35               | Vrms |

|                          | V <sub>IN</sub> 4 | HCTR                                                                                        | 0.035              |     | 0.35               | Vrms |

| Input voltage range      | V <sub>IN</sub> 5 | ADI0, ADI1, ADI2, ADI3                                                                      | 0                  |     | V <sub>DD</sub>    | V    |

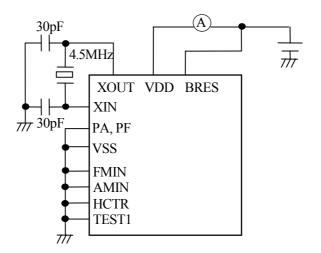

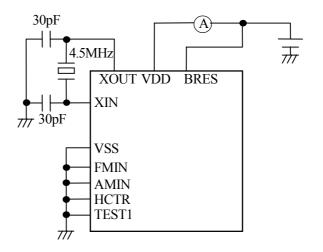

|                          | FIN1              | XIN                                                                                         | 4.0                | 4.5 | 5.0                | MHz  |

|                          | F <sub>IN</sub> 2 | FMIN: V <sub>IN</sub> 2, V <sub>DD</sub> 1                                                  | 10                 |     | 130                | MHz  |

| Innut from unnur         | FIN3              | FMIN: VIN3, VDD1                                                                            | 130                |     | 250                | MHz  |

| Input frequency          | F <sub>IN</sub> 4 | AMIN(H): V <sub>IN</sub> 2, V <sub>DD</sub> 1                                               | 2                  |     | 40                 | MHz  |

|                          | F <sub>IN</sub> 5 | AMIN(L): V <sub>IN</sub> 2, V <sub>DD</sub> 1                                               | 0.5                |     | 10                 | MHz  |

|                          | FIN6              | HCTR: VIN4, VDD1                                                                            | 0.4                |     | 15                 | MHz  |

## Allowable Operating Ranges at Ta = -20 to $+70^{\circ}C$ , $V_{DD} = 2.6$ to 5.5V

| Parameter                    | Symbol             | Conditions                                                                                               | Ratings               |                      |                     | Unit |

|------------------------------|--------------------|----------------------------------------------------------------------------------------------------------|-----------------------|----------------------|---------------------|------|

| i didificici                 | Gymbol             | Conditions                                                                                               | min                   | typ                  | max                 | Onit |

|                              | l <sub>IH</sub> 1  | XIN: $V_I = V_{DD} = 5.0V$                                                                               | 2.0                   | 5.0                  | 15                  | μA   |

| High-level input             | I <sub>IH</sub> 2  | FMIN, AMIN, HCTR: VI = V <sub>DD</sub> = 5.0V                                                            | 4.0                   | 10                   | 30                  | μA   |

| current                      | I <sub>IH</sub> 3  | Ports PA (pull-down resistors disabled), PC, PD, PF, PG, PH, and PK. BRES: VI = V <sub>DD</sub> = 5.0 V. |                       |                      | 3                   | μA   |

|                              | lı∟1               | $XIN: V_I = V_{DD} = V_{SS}$                                                                             | -2.0                  | -5.0                 | -15                 | μA   |

| Low-level input              | I <sub>IL</sub> 2  | FMIN, AMIN, HCTR: $V_I = V_{DD} = V_{SS}$                                                                | -4.0                  | -10                  | -30                 | μA   |

| current                      | I <sub>IL</sub> 3  | Ports PA (pull-down resistors disabled), PC, PD, PF, PG, PH, and PK. BRES: VI = VDD = VSS.               |                       |                      | -3                  | μA   |

| Input floating voltage       | VIF                | PA. Pull-down resistors enabled                                                                          |                       |                      | 0.05V <sub>DD</sub> | V    |

| Pull-down resistance         | R <sub>PD</sub> 1  | PA pull-down resistors. $V_{DD}$ = 5.0 V                                                                 | 75                    | 100                  | 200                 | kΩ   |

|                              | R <sub>PD</sub> 2  | TEST1 resistance                                                                                         |                       | 10                   |                     | kΩ   |

| Hysteresis                   | V <sub>H</sub>     | BRES                                                                                                     | 0.1V <sub>DD</sub>    |                      |                     | V    |

|                              | V <sub>OH</sub> 1  | PB: IO = 1mA                                                                                             | V <sub>DD</sub> -2.0  | V <sub>DD</sub> -1.0 |                     | V    |

|                              | V <sub>OH</sub> 2  | PC, PD, PE3, PG, PH, PK: I <sub>O</sub> = 1mA                                                            | V <sub>DD</sub> -1.0  |                      |                     | V    |

| High-level output            | VOH3               | EO: Ι <sub>Ο</sub> = 500μA                                                                               | V <sub>DD</sub> -1.0  |                      |                     | V    |

| voltage                      | VOH4               | XOUT: Ι <sub>O</sub> = 200μA                                                                             | V <sub>DD</sub> -1.0  |                      |                     | V    |

|                              | V <sub>OH</sub> 5  | S1 to S20: I <sub>O</sub> = 100μA                                                                        | V <sub>DD</sub> -1.0  |                      |                     | V    |

|                              | VOH6               | COM1, COM2, COM3, COM4: Ι <sub>O</sub> = 5μA                                                             | V <sub>DD</sub> -0.75 | V <sub>DD</sub> 0.5  |                     | V    |

|                              | V <sub>OL</sub> 1  | PB: Ι <sub>O</sub> = –50μA                                                                               |                       | 1.0                  | 2.0                 | V    |

|                              | Vol2               | PC, PD, PE3, PG, PH, PK: I <sub>O</sub> = -1mA                                                           |                       |                      | 1.0                 | V    |

|                              | VOL3               | EO: Ι <sub>Ο</sub> = -500μA                                                                              |                       |                      | 1.0                 | V    |

| Low-level output voltage     | V <sub>OL</sub> 4  | XOUT: I <sub>O</sub> = -200μA                                                                            |                       |                      | 1.0                 | V    |

| Vollage                      | VOL5               | S1 to S20: I <sub>O</sub> = -100μA                                                                       |                       |                      | 1.0                 | V    |

|                              | V <sub>OL</sub> 6  | COM1, COM2, COM3, COM4: Ι <sub>O</sub> = -5μA                                                            |                       | 0.5                  | 0.75                | V    |

|                              | V <sub>OL</sub> 7  | PE2, PL0 to PL3: IO = 5mA                                                                                |                       |                      | 2.0                 | V    |

| Output off leakage           | I <sub>OFF</sub> 1 | The PB, PC, PD, PE3, PG, PH, PK, and EO ports                                                            | -3                    |                      | +3                  | μA   |

| current                      | I <sub>OFF</sub> 2 | PE2, PL0 to PL3                                                                                          | -100                  |                      | +100                | nA   |

| Output mid-level voltage     | VM                 | COM1, COM2, COM3, COM4: V <sub>DD</sub> = 5.0V                                                           | 2.0                   | 2.5                  | 3.0                 | V    |

| A/D conversion error         |                    | ADI0, ADI1, ADI2, ADI3                                                                                   | -1/2                  |                      | +1/2                | LSB  |

| Power down detection voltage | VDET               |                                                                                                          | 2.7                   | 3.0                  | 3.3                 | V    |

|                              | I <sub>DD</sub> 1  | V <sub>DD</sub> 1: F <sub>IN</sub> 2 130MHz Ta = 25°C                                                    |                       | 15                   | 20                  | mA   |

| Oursearch alors in           | I <sub>DD</sub> 2  | V <sub>DD</sub> 3: Halt mode, Ta = 25°C *1                                                               |                       | 0.6                  |                     | mA   |

| Current drain                | IDD3               | V <sub>DD</sub> = 5.5 V, oscillator stopped, Ta = 25°C *2                                                |                       |                      | 5                   | μA   |

|                              | IDD4               | $V_{DD}$ = 2.5 V, oscillator stopped, Ta = 25°C *2                                                       |                       |                      | 1                   | μA   |

Note: The halt mode current is used to execute 20 instruction steps every 125 ms.

\*1 Halt and PLL stop mode current measurement conditions

With all ports other than those mentioned above left open. With output mode selected for PC and PD. With segment mode selected for S13 to S20.

Set up halt mode with a software instruction. The state where CPU operation is stopped without stopping the crystal oscillator.

\*2 Backup mode current measurement conditions

With all ports other than those mentioned above left open. With output mode selected for PC and PD. With segment mode selected for S13 to S20.

Set up backup mode with a software instruction. The state where the crystal oscillator is stopped.

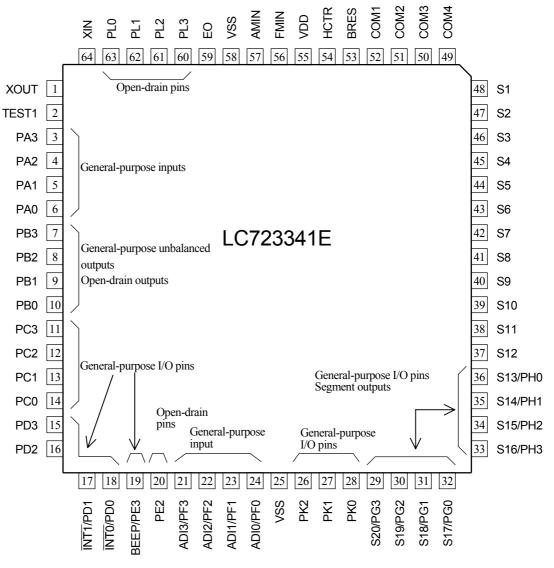

#### **Pin Assignment**

Top view

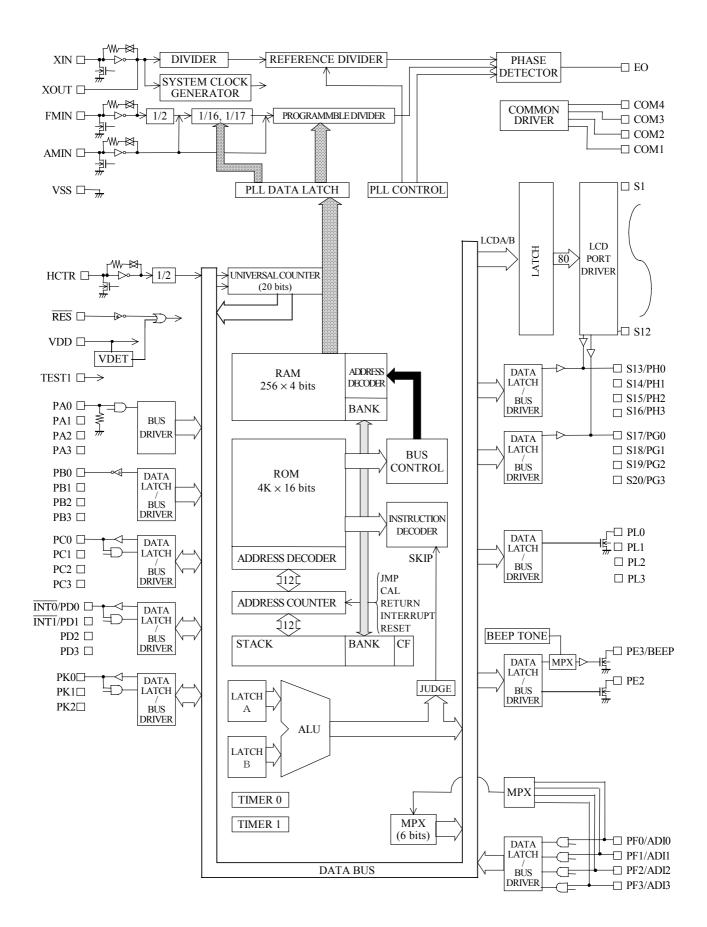

#### **Block Diagram**

### **Pin Functions**

| Pin No.              | Symbol                             | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Equivalent circuit                                             |

|----------------------|------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 64<br>1              | XIN<br>XOUT                        | 1<br>O | 4.5 MHz crystal oscillator circuit connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                |

| 2                    | TEST1                              | I      | IC test pin<br>This pin must be connected to ground during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                              |

| 6<br>5<br>4<br>3     | PA0<br>PA1<br>PA2<br>PA3           | I      | These input ports are used as the key return ports and are designed with a low threshold voltage. When a key matrix is formed with the PB port, multiple key presses with up to 3 keys can be detected. The four pull-down resistors are enabled/disabled together with an IOS instruction (PWn = 2, b1). The pull-down resistors cannot be controlled individually. In backup mode, this port goes to the input disabled state, and the pull-down resistors will be in the disabled state after a reset.                                                                                                                                                                                                | Input with built-in pull-down resistor                         |

| 10<br>9<br>8<br>7    | PB0<br>PB1<br>PB2<br>PB3           | o      | These output ports are used as the key source ports and can be set up to be either unbalanced outputs or open-drain outputs. The output type is set with an IOS instruction (PWn = 2, b0, b2, b3). When used set to the unbalanced output circuit type, diodes to prevent short circuits due to multiple key presses are not required. If used set to the open-drain output circuit type, pull-up resistors between VDD and the port pins are required. In backup mode, this port goes to the output high-impedance state. After a reset, this port will be in the output high-impedance state, and will remain in that state until an output instruction (an OUT, SPB, or RPB instruction) is executed. | Unbalanced CMOS push-pull<br>or<br>n-channel open-drain output |

| 15<br>14<br>13<br>12 | PC0<br>PC1<br>PC2<br>PC3           | VO     | General-purpose I/O ports. *1<br>The IOS instruction (PWN = 4) is used to switch between the general-purpose input and<br>output port functions. The I/O direction can be set in 1-bit units. (0: input, 1: output)<br>In backup mode, this port goes to the input disabled high-impedance state.<br>After a reset, the general-purpose input port function will be selected.                                                                                                                                                                                                                                                                                                                            | CMOS push-pull circuit                                         |

| 18<br>17<br>16<br>15 | PD0/INT0<br>PD1/INT1<br>PD2<br>PD3 | VO     | General-purpose I/O ports. *1<br>The IOS instruction (PWN = 5, b0, b1) is used to switch between the general-purpose input<br>and output port functions. The I/O direction can be set in 1-bit units. (0: input, 1: output)<br>Two of these port pins can be used as external interrupt inputs. In that case, the I/O<br>direction must be set to input, and rising or falling edge detection must be selected with an<br>IOS instruction (PWN = 3, b0, b1).<br>In backup mode, this port goes to the input disabled high-impedance state.<br>After a reset, the general-purpose input port function will be selected.                                                                                   | CMOS push-pull circuit                                         |

Note: \*1 When ports that can be switched between input and output are used as output ports, the output data must be established in advance with an OUT, SPB, or RPB instruction before the port is set to output mode with an IOS instruction.

Continued on next page.

## LC723341E

| Pin No.                                      | Symbol                                                                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Equivalent circuit          |

|----------------------------------------------|--------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 20                                           | PE2                                                                                  | 0   | PE2 is an open-drain output port. A pull-up resistor between this port and VDD is required.<br>In backup mode, PE2 goes to the high-impedance state. After a reset, it remains at the low<br>level until an output instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N-channel open-drain output |

| 18                                           | PE3/BEEP                                                                             | 0   | <ul> <li>General-purpose output or beep tone output shared-function port.</li> <li>The BEEP instruction is used to switch between the general-purpose output and beep tone output functions.</li> <li>To use this port as a general-purpose output port, execute a BEEP instruction with b3 = 0 to set up the general-purpose output function. If b3 = 1, the beep tone output function will be selected. Bits b0, b1, and b2 select the beep tone frequency. The LC723341E provides seven beep tone frequencies.</li> <li>*: When the PE3 port is set to the beep tone function, executing an output instruction only switches the state of the internal output latch and has no effect on the beep tone output.</li> <li>In backup mode, this port goes to the high-impedance state. This state is maintained until either an output instruction or a BEEP instruction secuted.</li> <li>After a reset, the general-purpose output port function will be selected.</li> </ul>                                                                                                                               | CMOS push-pull output       |

| 24<br>23<br>22<br>21                         | PF0/ADI0<br>PF1/ADI1<br>PF2/ADI2<br>PF3/ADI3                                         | I   | <ul> <li>General-purpose input or A/D converter input shared-function ports. The IOS instruction (PWn = FH, b0 to b3) is used to switch between the general-purpose input and A/D converter input functions. The function can be switched in 1-bit units. (0: general-purpose input, 1: A/D converter input)</li> <li>When the A/D converter input function is selected, the pin to be A/D converted is selected with the IOS instruction (PWn = 1). The A/D converter is started with the UCC instruction (b3 = 1, b2 = 1). The ADCE flag is set when the conversion completes. The INR instruction is used to read out the data.</li> <li>*: Since CMOS input is disabled, the data read out will always be zero if an input instruction is executed for a port pin set to analog input mode.</li> <li>Execute an IOS instruction (PWn = 0, b0 to b3) to set the port that clears backup mode. In backup mode, this port goes to input disabled high-impedance state. After a reset, the general-purpose input port function will be selected. The converter full-scale voltage is 63/96 of VDD.</li> </ul> | CMOS input or analog input  |

| 28<br>27<br>26                               | PK0<br>PK1<br>PK2                                                                    | VO  | These are general-purpose I/O ports. *1<br>The IOS instruction (PWN = A) is used to switch between the general-purpose input and<br>output port functions. The I/O direction can be set in 1-bit units. (0: input, 1: output)<br>In backup mode, this port goes to the input disabled high-impedance state.<br>After a reset, the general-purpose input port function will be selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CMOS push-pull circuit      |

| 32<br>31<br>30<br>29<br>36<br>35<br>34<br>33 | S17/PG0<br>S18/PG1<br>S19/PG2<br>S20/PG3<br>S13/PH0<br>S14/PH1<br>S15/PH2<br>S16/PH3 | VO  | LCD driver segment output or general-purpose I/O shared-function ports. *1<br>The IOS instruction is used to switch between the segment output and general-purpose I/O<br>functions and for I/O direction switching for the general-purpose port function.<br>• When used as segment output ports<br>PG port IOS instruction (PWn = B, b0 to b3) 0: Segment output<br>PH port IOS instruction (PWn = C, b0 to b3) 0: General-purpose I/O<br>These pins can be switched in 1-bit units.<br>• When used as general-purpose I/O ports<br>PG port IOS instruction (PWn = 6, b0 to b3) 0: Input<br>PH port IOS instruction (PWn = 6, b0 to b3) 0: Input<br>PH port IOS instruction (PWn = 7, b0 to b3) 1: Output<br>The I/O directions of these pins can be set in 1-bit units.<br>In backup mode, when used as general-purpose output ports, the pins go to the input<br>disabled high-impedance state. When used as segment outputs, these pins will be held<br>fixed at the low level.                                                                                                                          | CMOS push-pull circuit      |

Note: \*1 When ports that can be switched between input and output are used as output ports, the output data must be established in advance with an  $\ensuremath{\mathsf{OUT}}, \ensuremath{\mathsf{SPB}}, \ensuremath{\mathsf{or}}\xspace \ensuremath{\mathsf{RPB}}$  instruction before the port is set to output mode with an IOS instruction.

Continued on next page.

## LC723341E

| Continued from preceding page. |                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |  |  |  |  |

|--------------------------------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|

| Pin No.                        | Symbol                       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                      | Equivalent circuit     |  |  |  |  |

| 48-37                          | S1-S12                       | 0   | LCD driver segment output pins.<br>This driver implements 1/4-duty 1/2-bias drive.<br>The frame frequency is 75 Hz.<br>In backup mode, after a reset, and after an LCD off instruction has been executed, these<br>pins will be held fixed at the low level.                                                                                                                                                     | CMOS push-pull circuit |  |  |  |  |

| 62<br>61<br>60<br>59           | COM1<br>COM2<br>COM3<br>COM4 | 0   | LCD driver common output pins.<br>This driver implements 1/4-duty 1/2-bias drive.<br>The frame frequency is 75 Hz.<br>In backup mode, after a reset, and after an LCD off instruction has been executed, these<br>pins will be held fixed at the low level.                                                                                                                                                      |                        |  |  |  |  |

| 69                             | BRES                         |     | System reset pin.<br>If this pin is held low for at least one machine cycle during CPU operation or in halt mode,<br>the system will be reset and execution will continue with the program counter set to location<br>0.                                                                                                                                                                                         |                        |  |  |  |  |

| 54                             | HCTR                         | I   | Dedicated universal counter input port.• For frequency measurement, select frequency measurement mode with the UCD instruction (b3 = 0, b2 = 0) and start the counter with the UCC instruction. $UCS b3, b2$ Measurement imeMeasurement mode00HCTRFrequency0110108 ms1132 ms                                                                                                                                     | CMOS amplifier input   |  |  |  |  |

| 56                             | FMIN                         | I   | FM VCO (local oscillator) input.         This pin is selected using the PLL instruction CW1 field.                                                                                                                                                                                                                                                                                                               | CMOS amplifier input   |  |  |  |  |

| 57                             | AMIN                         | I   | CW1 b1, b0       Band         1       0       2 to 40 MHz (SW)         1       1       0.5 to 10 MHz (MW,LW)                                                                                                                                                                                                                                                                                                     |                        |  |  |  |  |

| 59                             | EO                           | 0   | This is the main charge pump output. When the frequency of the local oscillator divided by<br>N is higher than the reference frequency, a high level is output, and when it is lower, a low<br>level is output. This pin goes to the high-impedance state when the frequencies match.<br>This pin goes to the output high-impedance state in backup mode, in halt mode, during a<br>reset, and in PLL stop mode. | CMOS push-pull circuit |  |  |  |  |

Continued on next page.

## LC723341E

#### Continued from preceding page.

| Pin No.              | Symbol                   | I/O | Description                                                                                                                                                                                                                                                | Equivalent circuit          |

|----------------------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 63<br>62<br>61<br>60 | PL0<br>PL1<br>PL2<br>PL3 | 0   | Open-drain output port. Pull-up resistors must be inserted between these port pins<br>and VDD.<br>These pins go to the high-impedance state in backup mode. After a reset, the output<br>remains at the low level until an output instruction is executed. | N-channel open-drain output |

| 25<br>58<br>55       | VSS<br>VSS<br>VDD        | _   | Power supply connections.<br>Connect the VSS pins to the minus side (ground) of the power supply.<br>Connect the VDD pin to the plus side.                                                                                                                 | _                           |

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, of otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 2004. Specifications and information herein are subject to change without notice.